## 8085A/8085A-2 SINGLE CHIP 8-BIT N-CHANNEL MICROPROCESSORS

- Single +5V Power Supply

- 100% Software Compatible with 8080A

- 1.3  $\mu$ s Instruction Cycle (8085A);

0.8  $\mu$ s (8085A-2)

- On-Chip Clock Generator (with External Crystal, LC or RC Network)

- On-Chip System Controller; Advanced Cycle Status Information Available for Large System Control

- Four Vectored Interrupt Inputs (One Is Non-Maskable) Plus an 8080A-Compatible Interrupt

- Serial In/Serial Out Port

- Decimal, Binary and Double Precision Arithmetic

- Direct Addressing Capability to 64k Bytes of Memory

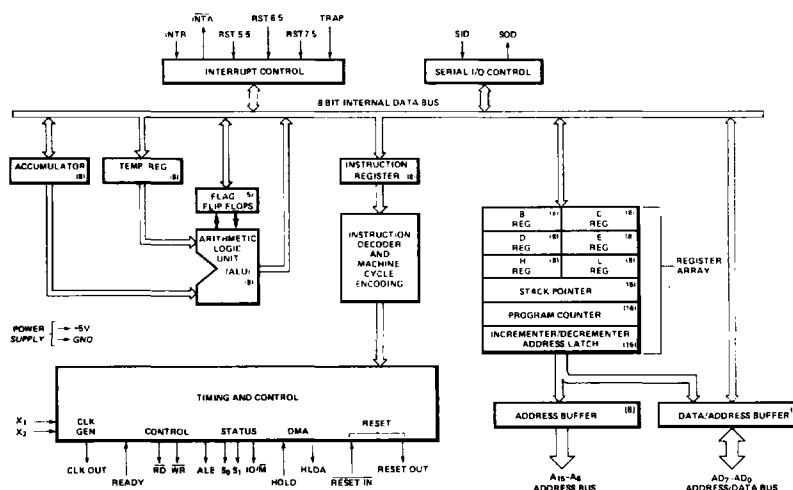

The Intel® 8085A is a complete 8 bit parallel Central Processing Unit (CPU). Its instruction set is 100% software compatible with the 8080A microprocessor, and it is designed to improve the present 8080A's performance by higher system speed. Its high level of system integration allows a minimum system of three IC's [8085A (CPU), 8156 (RAM/IO) and 8355/8755A (ROM/PROM/IO)] while maintaining total system expandability. The 8085A-2 is a faster version of the 8085A.

The 8085A incorporates all of the features that the 8224 (clock generator) and 8228 (system controller) provided for the 8080A, thereby offering a high level of system integration.

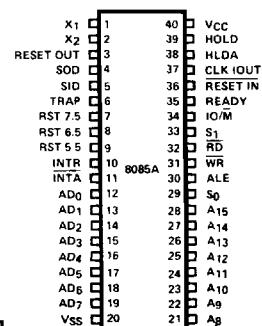

The 8085A uses a multiplexed data bus. The address is split between the 8 bit address bus and the 8 bit data bus. The on-chip address latches of 8155/8156/8355/8755A memory products allow a direct interface with the 8085A.

Figure 1. 8085A CPU Functional Block Diagram

Figure 2. 8085A Pin Configuration

**ABSOLUTE MAXIMUM RATINGS\***

|                                          |                 |

|------------------------------------------|-----------------|

| Ambient Temperature Under Bias . . . . . | 0°C to 70°C     |

| Storage Temperature . . . . .            | -65°C to +150°C |

| Voltage on Any Pin                       |                 |

| With Respect to Ground . . . . .         | -0.5V to +7V    |

| Power Dissipation . . . . .              | 1.5 Watt        |

*\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.*

**D.C. CHARACTERISTICS** ( $T_A = 0^\circ\text{C}$  to  $70^\circ\text{C}$ ,  $V_{CC} = 0\text{V} \pm 5\%$ ,  $V_{SS} = 0\text{V}$ ; unless otherwise specified)

| Symbol    | Parameter               | Min. | Max.           | Units         | Test Conditions                         |

|-----------|-------------------------|------|----------------|---------------|-----------------------------------------|

| $V_{IL}$  | Input Low Voltage       | -0.5 | +0.8           | V             |                                         |

| $V_{IH}$  | Input High Voltage      | 2.0  | $V_{CC} + 0.5$ | V             |                                         |

| $V_{OL}$  | Output Low Voltage      |      | 0.45           | V             | $I_{OL} = 2\text{mA}$                   |

| $V_{OH}$  | Output High Voltage     | 2.4  |                | V             | $I_{OH} = -400\mu\text{A}$              |

| $I_{CC}$  | Power Supply Current    |      | 170            | mA            |                                         |

| $I_{IL}$  | Input Leakage           |      | $\pm 10$       | $\mu\text{A}$ | $0 \leq V_{IN} \leq V_{CC}$             |

| $I_{LO}$  | Output Leakage          |      | $\pm 10$       | $\mu\text{A}$ | $0.45\text{V} \leq V_{out} \leq V_{CC}$ |

| $V_{ILR}$ | Input Low Level, RESET  | -0.5 | +0.8           | V             |                                         |

| $V_{IHR}$ | Input High Level, RESET | 2.4  | $V_{CC} + 0.5$ | V             |                                         |

| $V_{HY}$  | Hysteresis, RESET       | 0.25 |                | V             |                                         |

## A.C. CHARACTERISTICS (TA = 0°C to 70°C, VCC = 0V ±5%, VSS = 0V)

| Symbol                          | Parameter                                                          | 8085A <sup>[2]</sup> |      | 8085A-2 <sup>[2]</sup> |      | Units |

|---------------------------------|--------------------------------------------------------------------|----------------------|------|------------------------|------|-------|

|                                 |                                                                    | Min.                 | Max. | Min.                   | Max. |       |

| t <sub>CYC</sub>                | CLK Cycle Period                                                   | 320                  | 2000 | 200                    | 2000 | ns    |

| t <sub>1</sub>                  | CLK Low Time (Standard CLK Loading)                                | 80                   |      | 40                     |      | ns    |

| t <sub>2</sub>                  | CLK High Time (Standard CLK Loading)                               | 120                  |      | 70                     |      | ns    |

| t <sub>r</sub> , t <sub>f</sub> | CLK Rise and Fall Time                                             |                      | 30   |                        | 30   | ns    |

| t <sub>XKR</sub>                | X <sub>1</sub> Rising to CLK Rising                                | 30                   | 120  | 30                     | 100  | ns    |

| t <sub>XKF</sub>                | X <sub>1</sub> Rising to CLK Falling                               | 30                   | 150  | 30                     | 110  | ns    |

| t <sub>AC</sub>                 | A <sub>8-15</sub> Valid to Leading Edge of Control <sup>[1]</sup>  | 270                  |      | 115                    |      | ns    |

| t <sub>ACL</sub>                | A <sub>0-7</sub> Valid to Leading Edge of Control                  | 240                  |      | 115                    |      | ns    |

| t <sub>AD</sub>                 | A <sub>0-15</sub> Valid to Valid Data In                           |                      | 575  |                        | 350  | ns    |

| t <sub>AFR</sub>                | Address Float After Leading Edge of READ (INTA)                    |                      | 0    |                        | 0    | ns    |

| t <sub>AL</sub>                 | A <sub>8-15</sub> Valid Before Trailing Edge of ALE <sup>[1]</sup> | 115                  |      | 50                     |      | ns    |

| t <sub>ALL</sub>                | A <sub>0-7</sub> Valid Before Trailing Edge of ALE                 | 90                   |      | 50                     |      | ns    |

| t <sub>ARY</sub>                | READY Valid from Address Valid                                     |                      | 220  |                        | 100  | ns    |

| t <sub>CA</sub>                 | Address (A <sub>8-15</sub> ) Valid After Control                   | 120                  |      | 60                     |      | ns    |

| t <sub>CC</sub>                 | Width of Control Low (RD, WR, INTA) Edge of ALE                    | 400                  |      | 230                    |      | ns    |

| t <sub>CL</sub>                 | Trailing Edge of Control to Leading Edge of ALE                    | 50                   |      | 25                     |      | ns    |

| t <sub>DW</sub>                 | Data Valid to Trailing Edge of WRITE                               | 420                  |      | 230                    |      | ns    |

| t <sub>HABE</sub>               | HLDA to Bus Enable                                                 |                      | 210  |                        | 150  | ns    |

| t <sub>HABF</sub>               | Bus Float After HLDA                                               |                      | 210  |                        | 150  | ns    |

| t <sub>HACK</sub>               | HLDA Valid to Trailing Edge of CLK                                 | 110                  |      | 40                     |      | ns    |

| t <sub>HDH</sub>                | HOLD Hold Time                                                     | 0                    |      | 0                      |      | ns    |

| t <sub>HD5</sub>                | HOLD Setup Time to Trailing Edge of CLK                            | 170                  |      | 120                    |      | ns    |

| t <sub>INH</sub>                | INTR Hold Time                                                     | 0                    |      | 0                      |      | ns    |

| t <sub>INS</sub>                | INTR, RST, and TRAP Setup Time to Falling Edge of CLK              | 160                  |      | 150                    |      | ns    |

| t <sub>IA</sub>                 | Address Hold Time After ALE                                        | 100                  |      | 50                     |      | ns    |

| t <sub>LC</sub>                 | Trailing Edge of ALE to Leading Edge of Control                    | 130                  |      | 60                     |      | ns    |

| t <sub>LCK</sub>                | ALE Low During CLK High                                            | 100                  |      | 50                     |      | ns    |

| t <sub>LDR</sub>                | ALE to Valid Data During Read                                      |                      | 460  |                        | 270  | ns    |

| t <sub>LDW</sub>                | ALE to Valid Data During Write                                     |                      | 200  |                        | 120  | ns    |

| t <sub>LL</sub>                 | ALE Width                                                          | 140                  |      | 80                     |      | ns    |

| t <sub>LR</sub>                 | ALE to READY Stable                                                |                      | 110  |                        | 30   | ns    |

## A.C. CHARACTERISTICS (Continued)

| Symbol    | Parameter                                                   | 8085A <sup>[2]</sup> |      | 8085A-2 <sup>[2]</sup> |      | Units |

|-----------|-------------------------------------------------------------|----------------------|------|------------------------|------|-------|

|           |                                                             | Min.                 | Max. | Min.                   | Max. |       |

| $t_{RAE}$ | Trailing Edge of <u>READ</u> to Re-Enabling of Address      | 150                  |      | 90                     |      | ns    |

| $t_{RD}$  | <u>READ</u> (or <u>INTA</u> ) to Valid Data                 |                      | 300  |                        | 150  | ns    |

| $t_{RV}$  | Control Trailing Edge to Leading Edge of Next Control       | 400                  |      | 220                    |      | ns    |

| $t_{RDH}$ | Data Hold Time After <u>READ</u> <u>INTA</u> <sup>[7]</sup> | 0                    |      | 0                      |      | ns    |

| $t_{RYH}$ | <u>READY</u> Hold Time                                      | 0                    |      | 0                      |      | ns    |

| $t_{RYS}$ | <u>READY</u> Setup Time to Leading Edge of <u>CLK</u>       | 110                  |      | 100                    |      | ns    |

| $t_{WD}$  | Data Valid After Trailing Edge of <u>WRITE</u>              | 100                  |      | 60                     |      | ns    |

| $t_{WDL}$ | <u>LEADING</u> Edge of <u>WRITE</u> to Data Valid           |                      | 40   |                        | 20   | ns    |

## NOTES:

1. A<sub>8</sub>-A<sub>15</sub> address Specs apply to IO/M, S<sub>0</sub>, and S<sub>1</sub> except A<sub>8</sub>-A<sub>15</sub> are undefined during T<sub>4</sub>-T<sub>6</sub> of OF cycle whereas IO/M, S<sub>0</sub>, and S<sub>1</sub> are stable.

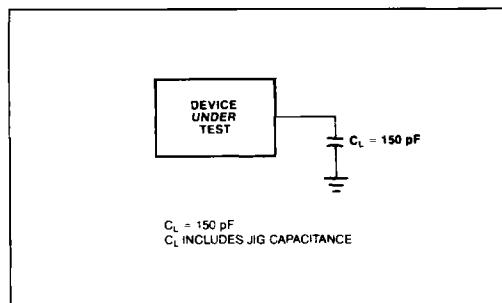

2. Test conditions: t<sub>CYC</sub> = 320 ns (8085A)/200 ns (8085A-2); C<sub>L</sub> = 150 pF.

3. For all output timing where C<sub>L</sub> = 150 pF use the following correction factors:

25 pF < C<sub>L</sub> < 150 pF: -0.10 ns/pF

150 pF < C<sub>L</sub> < 300 pF: +0.30 ns/pF

4. Output timings are measured with purely capacitive load.

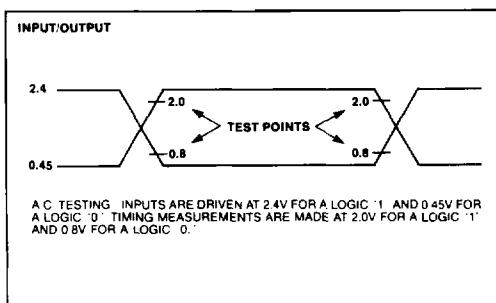

5. All timings are measured at output voltage V<sub>L</sub> = 0.8V, V<sub>H</sub> = 2.0V, and 1.5V with 20 ns rise and fall time on inputs.

6. To calculate timing specifications at other values of t<sub>CYC</sub> use Table 7.

7. Data hold time is guaranteed under all loading conditions.

## A.C. TESTING INPUT, OUTPUT WAVEFORM

## A.C. TESTING LOAD CIRCUIT