## 2.4-GHz *Bluetooth*™ low energy and Proprietary System-on-Chip

Check for Samples: [CC2541](#)

### FEATURES

- **RF**

- 2.4-GHz *Bluetooth* low energy Compliant and Proprietary RF System-on-Chip

- Supports 250-kbps, 500-kbps, 1-Mbps, 2-Mbps Data Rates

- Excellent Link Budget, Enabling Long-Range Applications Without External Front End

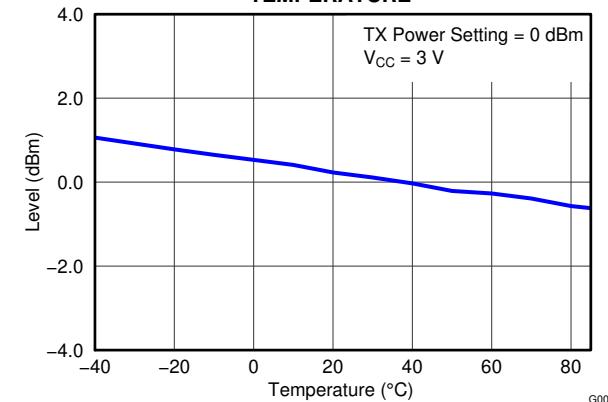

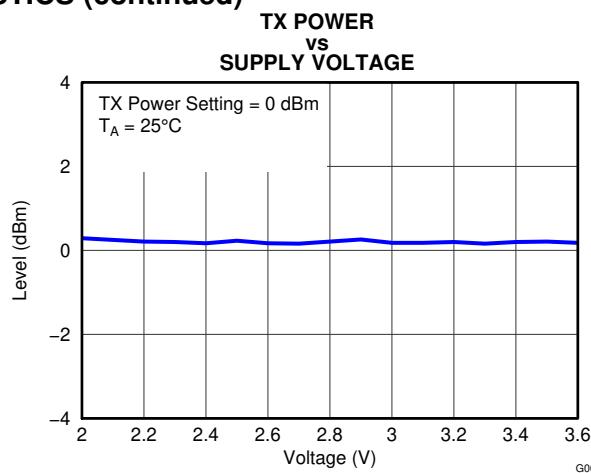

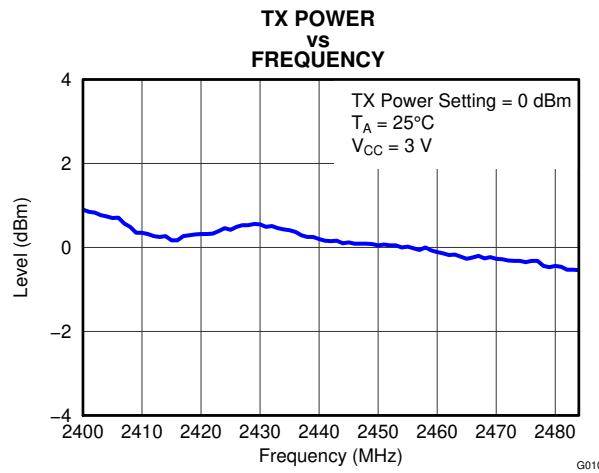

- Programmable Output Power up to 0 dBm

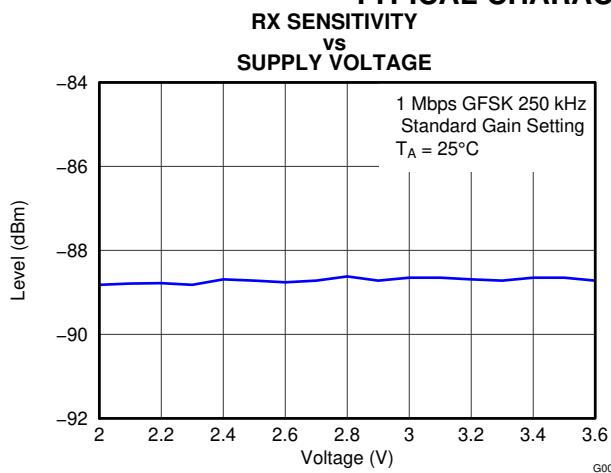

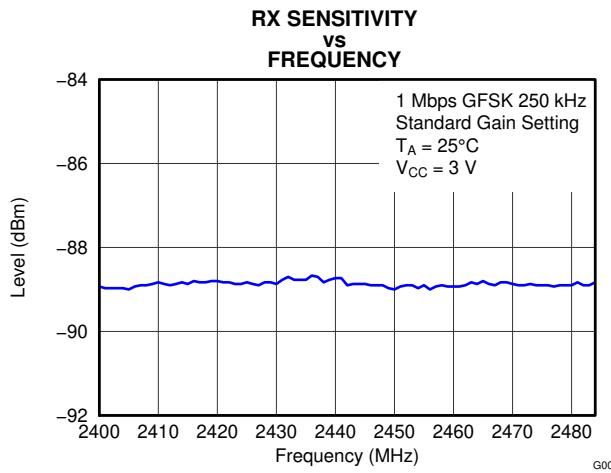

- Excellent Receiver Sensitivity ( $-94$  dBm at 1 Mbps), Selectivity, and Blocking Performance

- Suitable for Systems Targeting Compliance With Worldwide Radio Frequency Regulations: ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US), and ARIB STD-T66 (Japan)

- **Layout**

- Few External Components

- Reference Design Provided

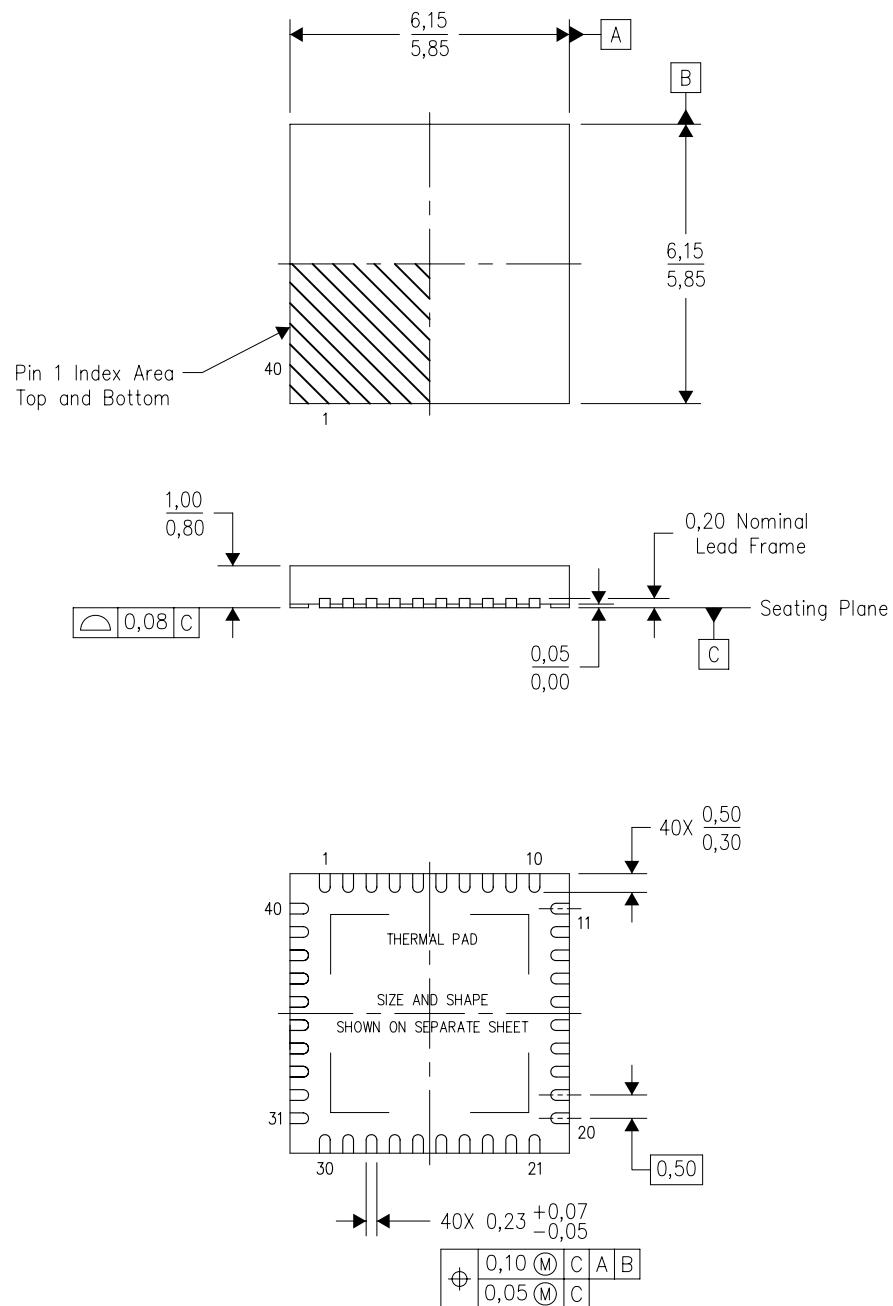

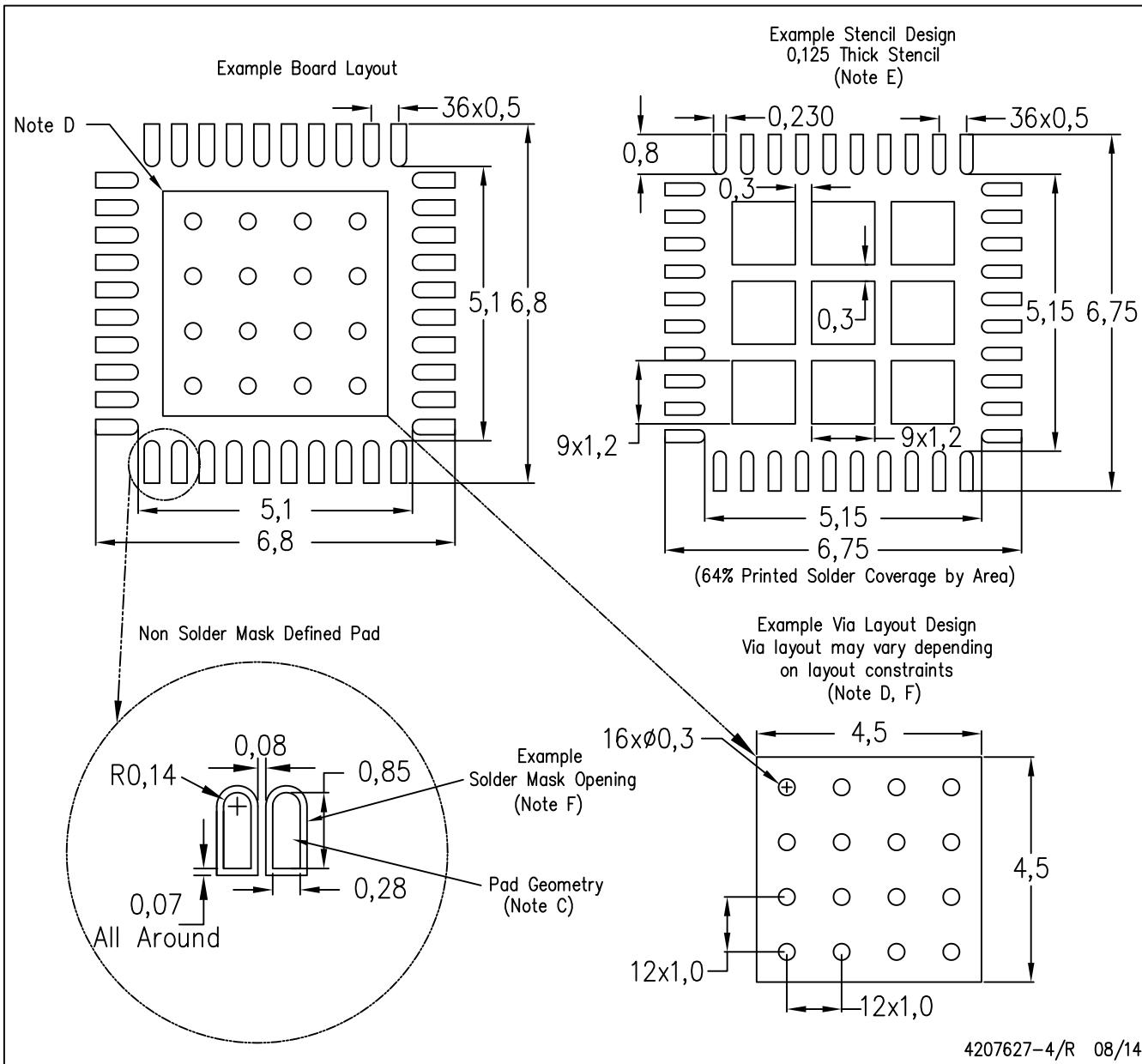

- 6-mm × 6-mm QFN-40 Package

- Pin-Compatible With CC2540 (When Not Using USB or I<sup>2</sup>C)

- **Low Power**

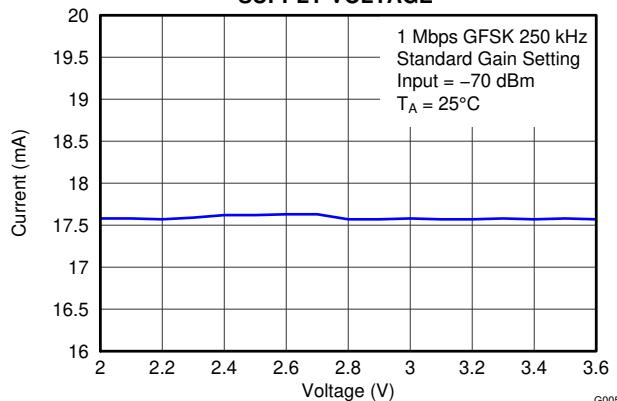

- Active-Mode RX Down to: 17.9 mA

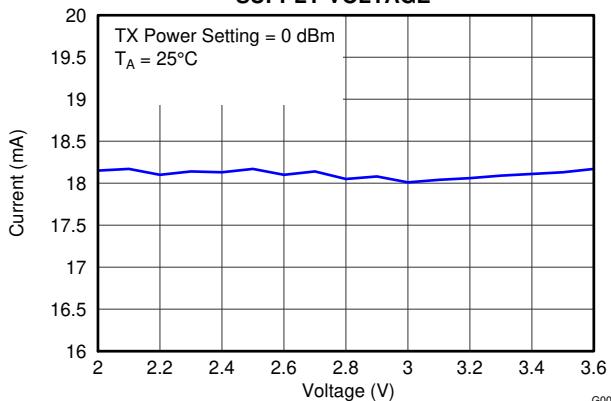

- Active-Mode TX (0 dBm): 18.2 mA

- Power Mode 1 (4- $\mu$ s Wake-Up): 270  $\mu$ A

- Power Mode 2 (Sleep Timer On): 1  $\mu$ A

- Power Mode 3 (External Interrupts): 0.5  $\mu$ A

- Wide Supply-Voltage Range (2 V–3.6 V)

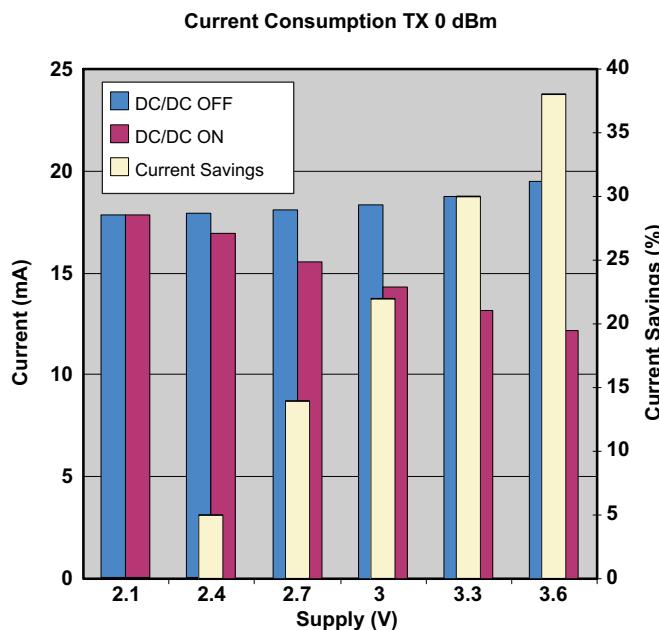

- **TPS62730** Compatible Low Power in Active Mode

- RX Down to: 14.7 mA (3-V supply)

- TX (0 dBm): 14.3 mA (3-V supply)

- **Microcontroller**

- High-Performance and Low-Power 8051 Microcontroller Core With Code Prefetch

- In-System-Programmable Flash, 128- or 256-KB

- 8-KB RAM With Retention in All Power Modes

- Hardware Debug Support

- Extensive Baseband Automation, Including Auto-Acknowledgment and Address Decoding

- Retention of All Relevant Registers in All Power Modes

- **Peripherals**

- Powerful Five-Channel DMA

- General-Purpose Timers (One 16-Bit, Two 8-Bit)

- IR Generation Circuitry

- 32-kHz Sleep Timer With Capture

- Accurate Digital RSSI Support

- Battery Monitor and Temperature Sensor

- 12-Bit ADC With Eight Channels and Configurable Resolution

- AES Security Coprocessor

- Two Powerful USARTs With Support for Several Serial Protocols

- 23 General-Purpose I/O Pins (21 × 4 mA, 2 × 20 mA)

- I<sup>2</sup>C interface

- 2 I/O Pins Have LED Driving Capabilities

- Watchdog Timer

- Integrated High-Performance Comparator

- **Development Tools**

- CC2541 Evaluation Module Kit (CC2541EMK)

- CC2541 Mini Development Kit (CC2541DK-MINI)

- SmartRF™ Software

- IAR Embedded Workbench™ Available

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Bluetooth is a trademark of Bluetooth SIG, Inc.

ZigBee is a registered trademark of ZigBee Alliance.

## SOFTWARE FEATURES

- **Bluetooth v4.0 Compliant Protocol Stack for Single-Mode BLE Solution**

- Complete Power-Optimized Stack, Including Controller and Host

- GAP – Central, Peripheral, Observer, or Broadcaster (Including Combination Roles)

- ATT / GATT – Client and Server

- SMP – AES-128 Encryption and Decryption

- L2CAP

- Sample Applications and Profiles

- Generic Applications for GAP Central and Peripheral Roles

- Proximity, Accelerometer, Simple Keys, and Battery GATT Services

- More Applications Supported in **BLE Software Stack**

- Multiple Configuration Options

- Single-Chip Configuration, Allowing Applications to Run on CC2541

- Network Processor Interface for Applications Running on an External Microcontroller

- BTool – Windows PC Application for Evaluation, Development, and Test

## APPLICATIONS

- 2.4-GHz **Bluetooth low energy Systems**

- Proprietary 2.4-GHz Systems

- Human-Interface Devices (Keyboard, Mouse, Remote Control)

- Sports and Leisure Equipment

- Mobile Phone Accessories

- Consumer Electronics

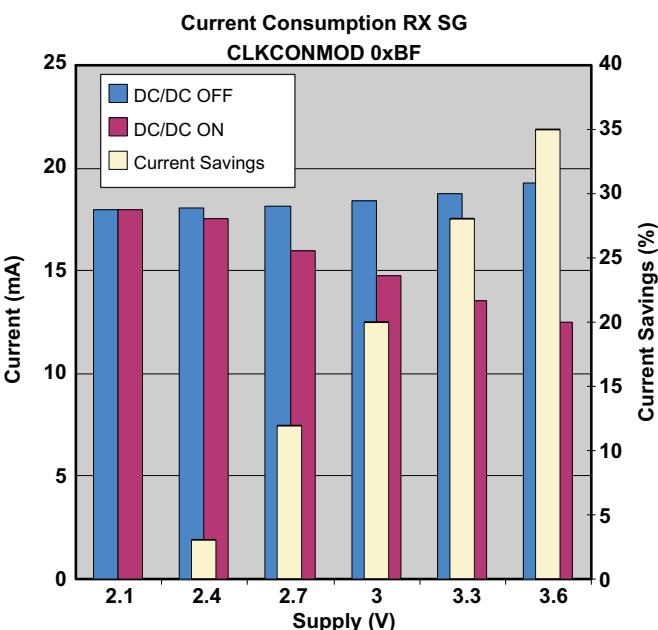

## CC2541 WITH **TPS62730**

- **TPS62730** is a 2-MHz Step-Down Converter With Bypass Mode

- Extends Battery Lifetime by up to 20%

- Reduced Current in All Active Modes

- 30-nA Bypass Mode Current to Support Low-Power Modes

- RF Performance Unchanged

- Small Package Allows for Small Solution Size

- CC2541 Controllable

## DESCRIPTION

The CC2541 is a power-optimized true system-on-chip (SoC) solution for both *Bluetooth* low energy and proprietary 2.4-GHz applications. It enables robust network nodes to be built with low total bill-of-material costs. The CC2541 combines the excellent performance of a leading RF transceiver with an industry-standard enhanced 8051 MCU, in-system programmable flash memory, 8-KB RAM, and many other powerful supporting features and peripherals. The CC2541 is highly suited for systems where ultralow power consumption is required. This is specified by various operating modes. Short transition times between operating modes further enable low power consumption.

The CC2541 is pin-compatible with the CC2540 in the 6-mm × 6-mm QFN40 package, if the USB is not used on the CC2540 and the I<sup>2</sup>C/extra I/O is not used on the CC2541. Compared to the CC2540, the CC2541 provides lower RF current consumption. The CC2541 does not have the USB interface of the CC2540, and provides lower maximum output power in TX mode. The CC2541 also adds a HW I<sup>2</sup>C interface.

The CC2541 is pin-compatible with the CC2533 RF4CE-optimized IEEE 802.15.4 SoC.

The CC2541 comes in two different versions: CC2541F128/F256, with 128 KB and 256 KB of flash memory, respectively.

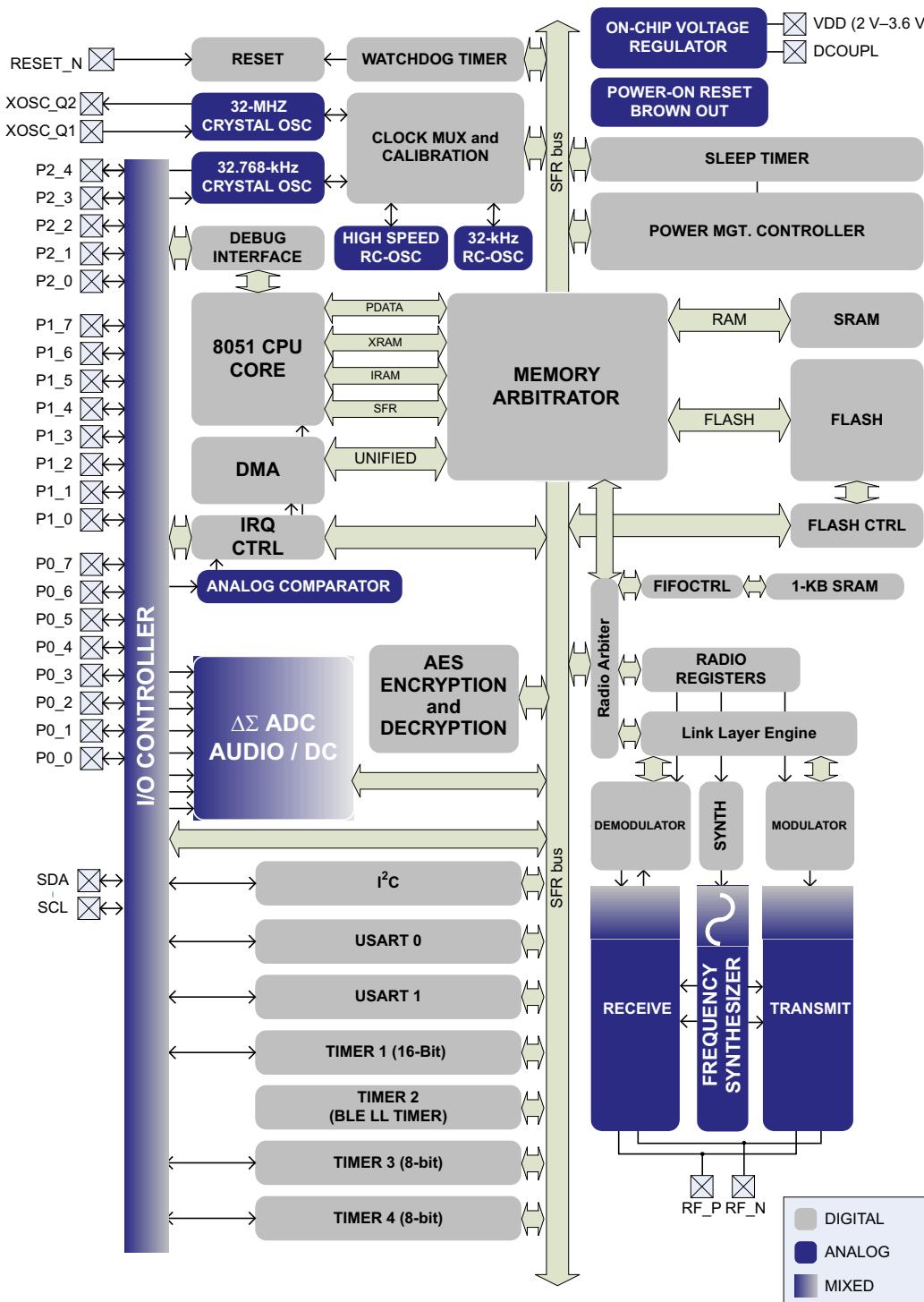

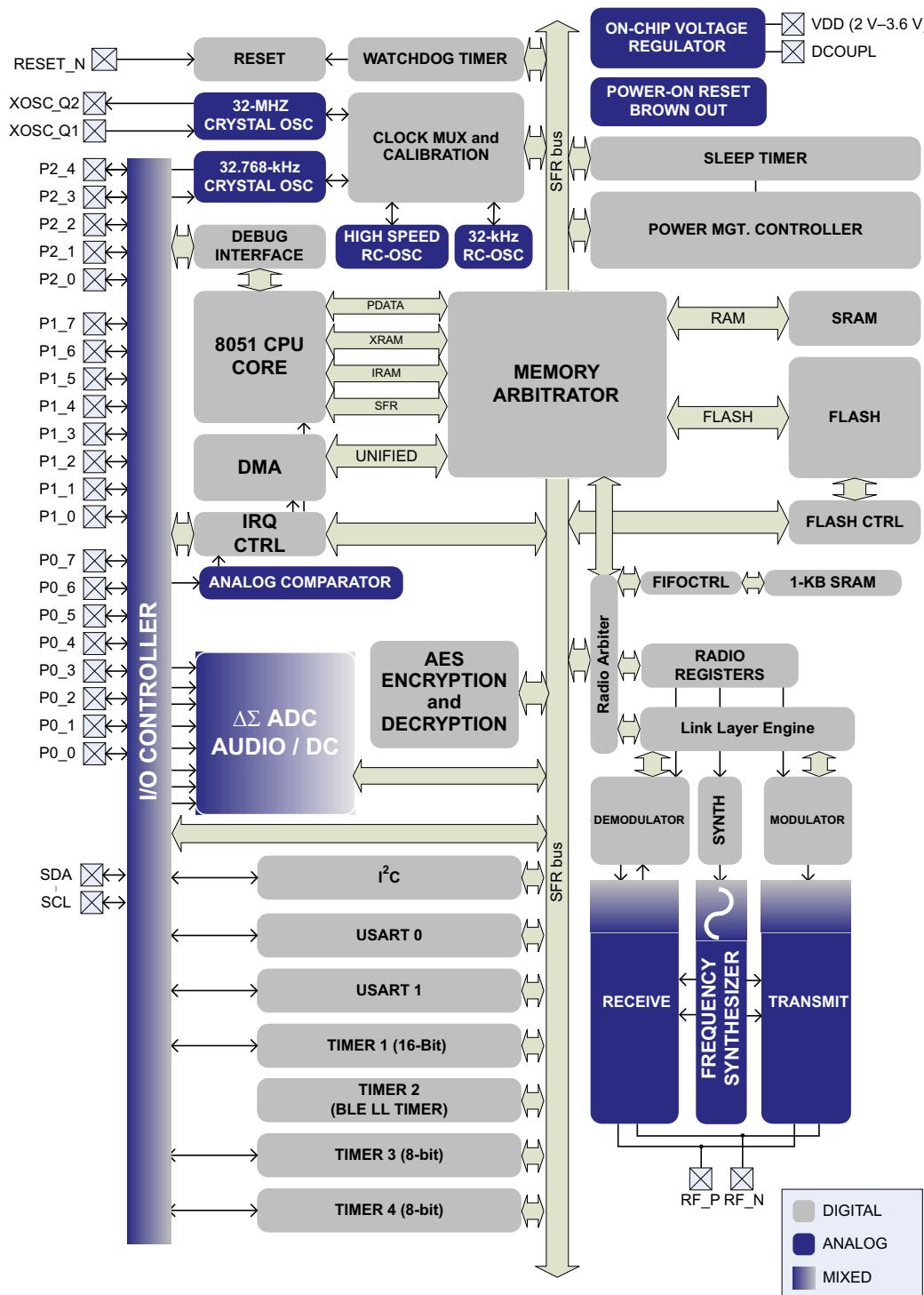

For the CC2541 block diagram, see [Figure 1](#).

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

**Figure 1. Block Diagram**

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                            |                                                                                              | MIN  | MAX             | UNIT |

|----------------------------|----------------------------------------------------------------------------------------------|------|-----------------|------|

| Supply voltage             | All supply pins must have the same voltage                                                   | -0.3 | 3.9             | V    |

| Voltage on any digital pin |                                                                                              | -0.3 | VDD + 0.3 ≤ 3.9 | V    |

| Input RF level             |                                                                                              |      | 10              | dBm  |

| Storage temperature range  |                                                                                              | -40  | 125             | °C   |

| ESD <sup>(2)</sup>         | All pins, excluding pins 25 and 26, according to human-body model, JEDEC STD 22, method A114 |      | 2               | kV   |

|                            | All pins, according to human-body model, JEDEC STD 22, method A114                           |      | 1               | kV   |

|                            | According to charged-device model, JEDEC STD 22, method C101                                 |      | 500             | V    |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) **CAUTION:** ESD sensitive device. Precautions should be used when handling the device in order to prevent permanent damage.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                            | MIN | NOM | MAX | UNIT |

|--------------------------------------------|-----|-----|-----|------|

| Operating ambient temperature range, $T_A$ | -40 | 85  |     | °C   |

| Operating supply voltage                   | 2   | 3.6 |     | V    |

## ELECTRICAL CHARACTERISTICS

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $\text{VDD} = 3\text{ V}$ ,

**1 Mbps, GFSK, 250-kHz deviation, Bluetooth low energy mode, and 0.1% BER**

| PARAMETER                                                                                                     | TEST CONDITIONS                                                                                                                                                  | MIN | TYP  | MAX | UNIT          |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------|

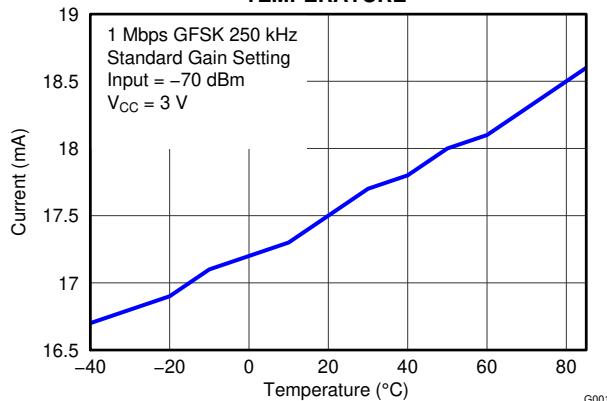

| $I_{\text{core}}$                                                                                             | RX mode, standard mode, no peripherals active, low MCU activity                                                                                                  |     | 17.9 |     | mA            |

|                                                                                                               | RX mode, high-gain mode, no peripherals active, low MCU activity                                                                                                 |     | 20.2 |     |               |

|                                                                                                               | TX mode, -20 dBm output power, no peripherals active, low MCU activity                                                                                           |     | 16.8 |     |               |

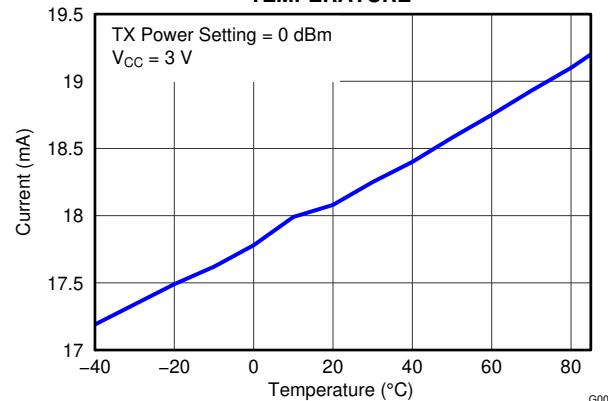

|                                                                                                               | TX mode, 0 dBm output power, no peripherals active, low MCU activity                                                                                             |     | 18.2 |     |               |

|                                                                                                               | Power mode 1. Digital regulator on; 16-MHz RCOSC and 32-MHz crystal oscillator off; 32.768-kHz XOSC, POR, BOD and sleep timer active; RAM and register retention |     | 270  |     | $\mu\text{A}$ |

|                                                                                                               | Power mode 2. Digital regulator off; 16-MHz RCOSC and 32-MHz crystal oscillator off; 32.768-kHz XOSC, POR, and sleep timer active; RAM and register retention    |     | 1    |     |               |

| $I_{\text{peri}}$                                                                                             | Power mode 3. Digital regulator off; no clocks; POR active; RAM and register retention                                                                           |     | 0.5  |     | mA            |

|                                                                                                               | Low MCU activity: 32-MHz XOSC running. No radio or peripherals. Limited flash access, no RAM access.                                                             |     | 6.7  |     |               |

|                                                                                                               | Timer 1. Timer running, 32-MHz XOSC used                                                                                                                         |     | 90   |     |               |

|                                                                                                               | Timer 2. Timer running, 32-MHz XOSC used                                                                                                                         |     | 90   |     | $\mu\text{A}$ |

|                                                                                                               | Timer 3. Timer running, 32-MHz XOSC used                                                                                                                         |     | 60   |     |               |

|                                                                                                               | Timer 4. Timer running, 32-MHz XOSC used                                                                                                                         |     | 70   |     |               |

| Peripheral current consumption<br>(Adds to core current $I_{\text{core}}$ for each peripheral unit activated) | Sleep timer, including 32.753-kHz RCOSC                                                                                                                          |     | 0.6  |     | mA            |

|                                                                                                               | ADC, when converting                                                                                                                                             |     | 1.2  |     |               |

## GENERAL CHARACTERISTICS

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                       | TEST CONDITIONS                                                                                                                                                                                                 | MIN  | TYP  | MAX | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| <b>WAKE-UP AND TIMING</b>       |                                                                                                                                                                                                                 |      |      |     |      |

| Power mode 1 → Active           | Digital regulator on, 16-MHz RCOSC and 32-MHz crystal oscillator off. Start-up of 16-MHz RCOSC                                                                                                                  | 4    |      |     | μs   |

| Power mode 2 or 3 → Active      | Digital regulator off, 16-MHz RCOSC and 32-MHz crystal oscillator off. Start-up of regulator and 16-MHz RCOSC                                                                                                   | 120  |      |     | μs   |

| Active → TX or RX               | Crystal ESR = 16 Ω. Initially running on 16-MHz RCOSC, with 32-MHz XOSC OFF                                                                                                                                     | 500  |      |     | μs   |

|                                 | With 32-MHz XOSC initially on                                                                                                                                                                                   | 180  |      |     | μs   |

| RX/TX turnaround                | Proprietary auto mode                                                                                                                                                                                           | 130  |      |     | μs   |

|                                 | BLE mode                                                                                                                                                                                                        | 150  |      |     |      |

| <b>RADIO PART</b>               |                                                                                                                                                                                                                 |      |      |     |      |

| RF frequency range              | Programmable in 1-MHz steps                                                                                                                                                                                     | 2379 | 2496 |     | MHz  |

| Data rate and modulation format | 2 Mbps, GFSK, 500-kHz deviation<br>2 Mbps, GFSK, 320-kHz deviation<br>1 Mbps, GFSK, 250-kHz deviation<br>1 Mbps, GFSK, 160-kHz deviation<br>500 kbps, MSK<br>250 kbps, GFSK, 160-kHz deviation<br>250 kbps, MSK |      |      |     |      |

## RF RECEIVE SECTION

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$ ,  $f_c = 2440\text{ MHz}$

| PARAMETER                                        | TEST CONDITIONS                                                                                         | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| <b>2 Mbps, GFSK, 500-kHz Deviation, 0.1% BER</b> |                                                                                                         |      |     |     |      |

| Receiver sensitivity                             |                                                                                                         | -90  |     |     | dBm  |

| Saturation                                       | BER < 0.1%                                                                                              | -1   |     |     | dBm  |

| Co-channel rejection                             | Wanted signal at -67 dBm                                                                                | -9   |     |     | dB   |

| In-band blocking rejection                       | ±2 MHz offset, 0.1% BER, wanted signal -67 dBm                                                          | -2   |     |     | dB   |

|                                                  | ±4 MHz offset, 0.1% BER, wanted signal -67 dBm                                                          | 36   |     |     |      |

|                                                  | ±6 MHz or greater offset, 0.1% BER, wanted signal -67 dBm                                               | 41   |     |     |      |

| Frequency error tolerance <sup>(1)</sup>         | Including both initial tolerance and drift. Sensitivity better than -67 dBm, 250 byte payload. BER 0.1% | -300 | 300 |     | kHz  |

| Symbol rate error tolerance <sup>(2)</sup>       | Maximum packet length. Sensitivity better than -67 dBm, 250 byte payload. BER 0.1%                      | -120 | 120 |     | ppm  |

| <b>2 Mbps, GFSK, 320-kHz Deviation, 0.1% BER</b> |                                                                                                         |      |     |     |      |

| Receiver sensitivity                             |                                                                                                         | -86  |     |     | dBm  |

| Saturation                                       | BER < 0.1%                                                                                              | -7   |     |     | dBm  |

| Co-channel rejection                             | Wanted signal at -67 dBm                                                                                | -12  |     |     | dB   |

| In-band blocking rejection                       | ±2 MHz offset, 0.1% BER, wanted signal -67 dBm                                                          | -1   |     |     | dB   |

|                                                  | ±4 MHz offset, 0.1% BER, wanted signal -67 dBm                                                          | 34   |     |     |      |

|                                                  | ±6 MHz or greater offset, 0.1% BER, wanted signal -67 dBm                                               | 39   |     |     |      |

| Frequency error tolerance <sup>(1)</sup>         | Including both initial tolerance and drift. Sensitivity better than -67 dBm, 250 byte payload. BER 0.1% | -300 | 300 |     | kHz  |

| Symbol rate error tolerance <sup>(2)</sup>       | Maximum packet length. Sensitivity better than -67 dBm, 250 byte payload. BER 0.1%                      | -120 | 120 |     | ppm  |

(1) Difference between center frequency of the received RF signal and local oscillator frequency

(2) Difference between incoming symbol rate and the internally generated symbol rate

## RF RECEIVE SECTION (continued)

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$ ,  $f_c = 2440\text{ MHz}$

| PARAMETER                                                                   | TEST CONDITIONS                                                                                         | MIN  | TYP | MAX | UNIT |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| <b>1 Mbps, GFSK, 250-kHz Deviation, Bluetooth low energy Mode, 0.1% BER</b> |                                                                                                         |      |     |     |      |

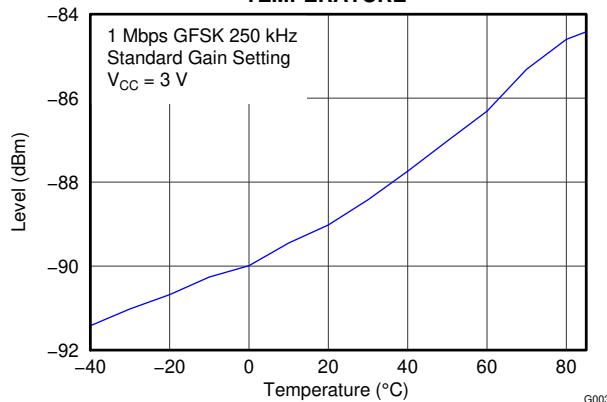

| Receiver sensitivity <sup>(3)(4)</sup>                                      | High-gain mode                                                                                          | –94  | dBm | –88 |      |

|                                                                             | Standard mode                                                                                           |      |     |     |      |

| Saturation <sup>(4)</sup>                                                   | BER < 0.1%                                                                                              | 5    |     |     | dBm  |

| Co-channel rejection <sup>(4)</sup>                                         | Wanted signal –67 dBm                                                                                   | –6   |     |     | dB   |

| In-band blocking rejection <sup>(4)</sup>                                   | ±1 MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | –2   | dB  |     |      |

|                                                                             | ±2 MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 26   |     |     |      |

|                                                                             | ±3 MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 34   |     |     |      |

|                                                                             | >6 MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 33   |     |     |      |

| Out-of-band blocking rejection <sup>(4)</sup>                               | Minimum interferer level < 2 GHz (Wanted signal –67 dBm)                                                | –21  | dBm |     |      |

|                                                                             | Minimum interferer level [2 GHz, 3 GHz] (Wanted signal –67 dBm)                                         | –25  |     |     |      |

|                                                                             | Minimum interferer level > 3 GHz (Wanted signal –67 dBm)                                                | –7   |     |     |      |

| Intermodulation <sup>(4)</sup>                                              | Minimum interferer level                                                                                | –36  |     |     | dBm  |

| Frequency error tolerance <sup>(5)</sup>                                    | Including both initial tolerance and drift. Sensitivity better than –67 dBm, 250 byte payload. BER 0.1% | –250 | 250 |     | kHz  |

| Symbol rate error tolerance <sup>(6)</sup>                                  | Maximum packet length. Sensitivity better than –67 dBm, 250 byte payload. BER 0.1%                      | –80  | 80  |     | ppm  |

| <b>1 Mbps, GFSK, 160-kHz Deviation, 0.1% BER</b>                            |                                                                                                         |      |     |     |      |

| Receiver sensitivity <sup>(7)</sup>                                         |                                                                                                         | –91  |     |     | dBm  |

| Saturation                                                                  | BER < 0.1%                                                                                              | 0    |     |     | dBm  |

| Co-channel rejection                                                        | Wanted signal 10 dB above sensitivity level                                                             | –9   |     |     | dB   |

| In-band blocking rejection                                                  | ±1-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 2    | dB  |     |      |

|                                                                             | ±2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 24   |     |     |      |

|                                                                             | ±3-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 27   |     |     |      |

|                                                                             | >6-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 32   |     |     |      |

| Frequency error tolerance <sup>(5)</sup>                                    | Including both initial tolerance and drift. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1% | –200 | 200 |     | kHz  |

| Symbol rate error tolerance <sup>(6)</sup>                                  | Maximum packet length. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1%                      | –80  | 80  |     | ppm  |

| <b>500 kbps, MSK, 0.1% BER</b>                                              |                                                                                                         |      |     |     |      |

| Receiver sensitivity <sup>(7)</sup>                                         |                                                                                                         | –99  |     |     | dBm  |

| Saturation                                                                  | BER < 0.1%                                                                                              | 0    |     |     | dBm  |

| Co-channel rejection                                                        | Wanted signal –67 dBm                                                                                   | –5   |     |     | dB   |

| In-band blocking rejection                                                  | ±1-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 20   | dB  |     |      |

|                                                                             | ±2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 27   |     |     |      |

|                                                                             | >2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 28   |     |     |      |

| Frequency error tolerance                                                   | Including both initial tolerance and drift. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1% | –150 | 150 |     | kHz  |

| Symbol rate error tolerance                                                 | Maximum packet length. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1%                      | –80  | 80  |     | ppm  |

- (3) The receiver sensitivity setting is programmable using a TI BLE stack vendor-specific API command. The default value is standard mode.

- (4) Results based on standard-gain mode.

- (5) Difference between center frequency of the received RF signal and local oscillator frequency

- (6) Difference between incoming symbol rate and the internally generated symbol rate

- (7) Results based on high-gain mode.

## RF RECEIVE SECTION (continued)

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$ ,  $f_c = 2440\text{ MHz}$

| PARAMETER                                          | TEST CONDITIONS                                                                                         | MIN  | TYP | MAX | UNIT |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| <b>250 kbps, GFSK, 160 kHz Deviation, 0.1% BER</b> |                                                                                                         |      |     |     |      |

| Receiver sensitivity <sup>(8)</sup>                |                                                                                                         | –98  |     |     | dBm  |

| Saturation                                         | BER < 0.1%                                                                                              | 0    |     |     | dBm  |

| Co-channel rejection                               | Wanted signal –67 dBm                                                                                   | –3   |     |     | dB   |

| In-band blocking rejection                         | ±1-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 23   |     |     | dB   |

|                                                    | ±2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 28   |     |     |      |

|                                                    | >2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 29   |     |     |      |

| Frequency error tolerance <sup>(9)</sup>           | Including both initial tolerance and drift. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1% | –150 | 150 |     | kHz  |

| Symbol rate error tolerance <sup>(10)</sup>        | Maximum packet length. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1%                      | –80  | 80  |     | ppm  |

| <b>250 kbps, MSK, 0.1% BER</b>                     |                                                                                                         |      |     |     |      |

| Receiver sensitivity <sup>(11)</sup>               |                                                                                                         | –99  |     |     | dBm  |

| Saturation                                         | BER < 0.1%                                                                                              | 0    |     |     | dBm  |

| Co-channel rejection                               | Wanted signal –67 dBm                                                                                   | –5   |     |     | dB   |

| In-band blocking rejection                         | ±1-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 20   |     |     | dB   |

|                                                    | ±2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 29   |     |     |      |

|                                                    | >2-MHz offset, 0.1% BER, wanted signal –67 dBm                                                          | 30   |     |     |      |

| Frequency error tolerance                          | Including both initial tolerance and drift. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1% | –150 | 150 |     | kHz  |

| Symbol rate error tolerance                        | Maximum packet length. Sensitivity better than –67 dBm, 250-byte payload. BER 0.1%                      | –80  | 80  |     | ppm  |

| <b>ALL RATES/FORMATS</b>                           |                                                                                                         |      |     |     |      |

| Spurious emission in RX. Conducted measurement     | f < 1 GHz                                                                                               | –67  |     |     | dBm  |

| Spurious emission in RX. Conducted measurement     | f > 1 GHz                                                                                               | –57  |     |     | dBm  |

(8) Results based on standard-gain mode.

(9) Difference between center frequency of the received RF signal and local oscillator frequency

(10) Difference between incoming symbol rate and the internally generated symbol rate

(11) Results based on high-gain mode.

## RF TRANSMIT SECTION

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$  and  $f_c = 2440\text{ MHz}$

| PARAMETER                               | TEST CONDITIONS                                                                                              | MIN                                                                                                                                                                                    | TYP | MAX      | UNIT |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|--|--|

| Output power                            | Delivered to a single-ended 50- $\Omega$ load through a balun using maximum recommended output power setting | 0                                                                                                                                                                                      | –23 | dBm      |      |  |  |

|                                         | Delivered to a single-ended 50- $\Omega$ load through a balun using minimum recommended output power setting |                                                                                                                                                                                        |     |          |      |  |  |

| Programmable output power range         | Delivered to a single-ended 50- $\Omega$ load through a balun using minimum recommended output power setting | 23                                                                                                                                                                                     |     | dB       |      |  |  |

| Spurious emission conducted measurement | $f < 1\text{ GHz}$                                                                                           | –52                                                                                                                                                                                    |     | dBm      |      |  |  |

|                                         | $f > 1\text{ GHz}$                                                                                           | –48                                                                                                                                                                                    |     | dBm      |      |  |  |

| Optimum load impedance                  |                                                                                                              | Suitable for systems targeting compliance with worldwide radio-frequency regulations ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US), and ARIB STD-T66 (Japan) |     | 70 +j30  |      |  |  |

| Optimum load impedance                  |                                                                                                              |                                                                                                                                                                                        |     | $\Omega$ |      |  |  |

Designs with antenna connectors that require conducted ETSI compliance at 64 MHz should insert an LC resonator in front of the antenna connector. Use a 1.6-nH inductor in parallel with a 1.8-pF capacitor. Connect both from the signal trace to a good RF ground.

## CURRENT CONSUMPTION WITH TPS62730

Measured on Texas Instruments CC2541 TPA62730 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$  and  $f_c = 2440\text{ MHz}$ , **1 Mbsp, GFSK, 250-kHz deviation, Bluetooth™ low energy Mode, 1% BER<sup>(1)</sup>**

| PARAMETER           | TEST CONDITIONS                                                                      | MIN  | TYP | MAX | UNIT |  |  |

|---------------------|--------------------------------------------------------------------------------------|------|-----|-----|------|--|--|

| Current consumption | RX mode, standard mode, no peripherals active, low MCU activity, MCU at 1 MHz        | 14.7 |     | mA  |      |  |  |

|                     | RX mode, high-gain mode, no peripherals active, low MCU activity, MCU at 1 MHz       | 16.7 |     |     |      |  |  |

|                     | TX mode, –20 dBm output power, no peripherals active, low MCU activity, MCU at 1 MHz | 13.1 |     |     |      |  |  |

|                     | TX mode, 0 dBm output power, no peripherals active, low MCU activity, MCU at 1 MHz   | 14.3 |     |     |      |  |  |

(1) 0.1% BER maps to 30.8% PER

## 32-MHz CRYSTAL OSCILLATOR

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                                      | MIN  | TYP | MAX | UNIT |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| Crystal frequency                                     |                                                                                                                                                                                                                      | 32   |     | MHz |      |

| Crystal frequency accuracy requirement <sup>(1)</sup> |                                                                                                                                                                                                                      | –40  |     | 40  |      |

| ESR                                                   | Equivalent series resistance                                                                                                                                                                                         | 6    |     | 60  |      |

| $C_0$                                                 | Crystal shunt capacitance                                                                                                                                                                                            | 1    |     | 7   |      |

| $C_L$                                                 | Crystal load capacitance                                                                                                                                                                                             | 10   |     | 16  |      |

| Start-up time                                         |                                                                                                                                                                                                                      | 0.25 |     | ms  |      |

| Power-down guard time                                 | The crystal oscillator must be in power down for a guard time before it is used again. This requirement is valid for all modes of operation. The need for power-down guard time can vary with crystal type and load. | 3    |     | ms  |      |

(1) Including aging and temperature dependency, as specified by [1]

## 32.768-kHz CRYSTAL OSCILLATOR

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                                             | TEST CONDITIONS              | MIN    | TYP | MAX | UNIT             |

|-------------------------------------------------------|------------------------------|--------|-----|-----|------------------|

| Crystal frequency                                     |                              | 32.768 |     |     | kHz              |

| Crystal frequency accuracy requirement <sup>(1)</sup> |                              | –40    | 40  | 40  | ppm              |

| ESR                                                   | Equivalent series resistance |        | 40  | 130 | $\text{k}\Omega$ |

| $C_0$                                                 | Crystal shunt capacitance    |        | 0.9 | 2   | $\text{pF}$      |

| $C_L$                                                 | Crystal load capacitance     |        | 12  | 16  | $\text{pF}$      |

| Start-up time                                         |                              | 0.4    |     |     | s                |

(1) Including aging and temperature dependency, as specified by [1]

## 32-kHz RC OSCILLATOR

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$ .

| PARAMETER                                 | TEST CONDITIONS | MIN    | TYP   | MAX | UNIT              |

|-------------------------------------------|-----------------|--------|-------|-----|-------------------|

| Calibrated frequency <sup>(1)</sup>       |                 | 32.753 |       |     | kHz               |

| Frequency accuracy after calibration      |                 |        | ±0.2% |     |                   |

| Temperature coefficient <sup>(2)</sup>    |                 | 0.4    |       |     | $^\circ/\text{C}$ |

| Supply-voltage coefficient <sup>(3)</sup> |                 | 3      |       |     | $^\circ/\text{V}$ |

| Calibration time <sup>(4)</sup>           |                 | 2      |       |     | ms                |

(1) The calibrated 32-kHz RC oscillator frequency is the 32-MHz XTAL frequency divided by 977.

(2) Frequency drift when temperature changes after calibration

(3) Frequency drift when supply voltage changes after calibration

(4) When the 32-kHz RC oscillator is enabled, it is calibrated when a switch from the 16-MHz RC oscillator to the 32-MHz crystal oscillator is performed while SLEEPCMD.OSC32K\_CALDIS is set to 0.

## 16-MHz RC OSCILLATOR

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                               | TEST CONDITIONS | MIN   | TYP | MAX | UNIT          |

|-----------------------------------------|-----------------|-------|-----|-----|---------------|

| Frequency <sup>(1)</sup>                |                 | 16    |     |     | MHz           |

| Uncalibrated frequency accuracy         |                 | ±18%  |     |     |               |

| Calibrated frequency accuracy           |                 | ±0.6% |     |     |               |

| Start-up time                           |                 | 10    |     |     | $\mu\text{s}$ |

| Initial calibration time <sup>(2)</sup> |                 | 50    |     |     | $\mu\text{s}$ |

(1) The calibrated 16-MHz RC oscillator frequency is the 32-MHz XTAL frequency divided by 2.

(2) When the 16-MHz RC oscillator is enabled, it is calibrated when a switch from the 16-MHz RC oscillator to the 32-MHz crystal oscillator is performed while SLEEPCMD.OSC\_PD is set to 0.

## RSSI CHARACTERISTICS

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                                                                                      | TEST CONDITIONS               | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|------|

| <b>2 Mbps, GFSK, 320-kHz Deviation, 0.1% BER and 2 Mbps, GFSK, 500-kHz Deviation, 0.1% BER</b> |                               |     |     |     |      |

| Useful RSSI range <sup>(1)</sup>                                                               | Reduced gain by AGC algorithm | 64  |     |     | dB   |

|                                                                                                | High gain by AGC algorithm    | 64  |     |     |      |

| RSSI offset <sup>(1)</sup>                                                                     | Reduced gain by AGC algorithm | 79  |     |     | dBm  |

|                                                                                                | High gain by AGC algorithm    | 99  |     |     |      |

| Absolute uncalibrated accuracy <sup>(1)</sup>                                                  |                               | ±6  |     |     | dB   |

| Step size (LSB value)                                                                          |                               | 1   |     |     | dB   |

| <b>All Other Rates/Formats</b>                                                                 |                               |     |     |     |      |

| Useful RSSI range <sup>(1)</sup>                                                               | Standard mode                 | 64  |     |     | dB   |

|                                                                                                | High-gain mode                | 64  |     |     |      |

| RSSI offset <sup>(1)</sup>                                                                     | Standard mode                 | 98  |     |     | dBm  |

|                                                                                                | High-gain mode                | 107 |     |     |      |

| Absolute uncalibrated accuracy <sup>(1)</sup>                                                  |                               | ±3  |     |     | dB   |

| Step size (LSB value)                                                                          |                               | 1   |     |     | dB   |

(1) Assuming CC2541 EM reference design. Other RF designs give an offset from the reported value.

## FREQUENCY SYNTHESIZER CHARACTERISTICS

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$  and  $f_c = 2440\text{ MHz}$

| PARAMETER                        | TEST CONDITIONS               | MIN  | TYP | MAX | UNIT   |

|----------------------------------|-------------------------------|------|-----|-----|--------|

| Phase noise, unmodulated carrier | At ±1-MHz offset from carrier | –109 |     |     | dBc/Hz |

|                                  | At ±3-MHz offset from carrier | –112 |     |     |        |

|                                  | At ±5-MHz offset from carrier | –119 |     |     |        |

## ANALOG TEMPERATURE SENSOR

Measured on Texas Instruments CC2541 EM reference design with  $T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                            | TEST CONDITIONS                                                                            | MIN  | TYP | MAX | UNIT   |

|--------------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|--------|

| Output                               |                                                                                            | 1480 |     |     | 12-bit |

| Temperature coefficient              |                                                                                            | 4.5  |     |     | / 1°C  |

| Voltage coefficient                  | Measured using integrated ADC, internal band-gap voltage reference, and maximum resolution | 1    |     |     | 0.1 V  |

| Initial accuracy without calibration |                                                                                            | ±10  |     |     | °C     |

| Accuracy using 1-point calibration   |                                                                                            | ±5   |     |     | °C     |

| Current consumption when enabled     |                                                                                            | 0.5  |     |     | mA     |

## COMPARATOR CHARACTERISTICS

$T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$ . All measurement results are obtained using the CC2541 reference designs, post-calibration.

| PARAMETER                   | TEST CONDITIONS | MIN  | TYP | MAX | UNIT  |

|-----------------------------|-----------------|------|-----|-----|-------|

| Common-mode maximum voltage |                 | VDD  |     |     | V     |

| Common-mode minimum voltage |                 | –0.3 |     |     |       |

| Input offset voltage        |                 | 1    |     |     | mV    |

| Offset vs temperature       |                 | 16   |     |     | µV/°C |

| Offset vs operating voltage |                 | 4    |     |     | mV/V  |

| Supply current              |                 | 230  |     |     | nA    |

| Hysteresis                  |                 | 0.15 |     |     | mV    |

## ADC CHARACTERISTICS

$T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                               |                                | TEST CONDITIONS                                                                    | MIN   | TYP   | MAX | UNIT             |

|-----------------------------------------|--------------------------------|------------------------------------------------------------------------------------|-------|-------|-----|------------------|

| Input voltage                           |                                | VDD is voltage on AVDD5 pin                                                        | 0     | VDD   |     | V                |

| External reference voltage              |                                | VDD is voltage on AVDD5 pin                                                        | 0     | VDD   |     | V                |

| External reference voltage differential |                                | VDD is voltage on AVDD5 pin                                                        | 0     | VDD   |     | V                |

| Input resistance, signal                |                                | Simulated using 4-MHz clock speed                                                  |       | 197   |     | $\text{k}\Omega$ |

| Full-scale signal <sup>(1)</sup>        |                                | Peak-to-peak, defines 0 dBFS                                                       |       | 2.97  |     | V                |

| ENOB <sup>(1)</sup>                     | Effective number of bits       | Single-ended input, 7-bit setting                                                  |       | 5.7   |     | bits             |

|                                         |                                | Single-ended input, 9-bit setting                                                  |       | 7.5   |     |                  |

|                                         |                                | Single-ended input, 10-bit setting                                                 |       | 9.3   |     |                  |

|                                         |                                | Single-ended input, 12-bit setting                                                 |       | 10.3  |     |                  |

|                                         |                                | Differential input, 7-bit setting                                                  |       | 6.5   |     |                  |

|                                         |                                | Differential input, 9-bit setting                                                  |       | 8.3   |     |                  |

|                                         |                                | Differential input, 10-bit setting                                                 |       | 10    |     |                  |

|                                         |                                | Differential input, 12-bit setting                                                 |       | 11.5  |     |                  |

|                                         |                                | 10-bit setting, clocked by RCOSC                                                   |       | 9.7   |     |                  |

|                                         |                                | 12-bit setting, clocked by RCOSC                                                   |       | 10.9  |     |                  |

| Useful power bandwidth                  |                                | 7-bit setting, both single and differential                                        | 0–20  |       |     | $\text{kHz}$     |

| THD                                     | Total harmonic distortion      | Single ended input, 12-bit setting, –6 dBFS <sup>(1)</sup>                         | –75.2 |       |     | dB               |

|                                         |                                | Differential input, 12-bit setting, –6 dBFS <sup>(1)</sup>                         | –86.6 |       |     |                  |

| Signal to nonharmonic ratio             |                                | Single-ended input, 12-bit setting <sup>(1)</sup>                                  | 70.2  |       |     | dB               |

|                                         |                                | Differential input, 12-bit setting <sup>(1)</sup>                                  | 79.3  |       |     |                  |

|                                         |                                | Single-ended input, 12-bit setting, –6 dBFS <sup>(1)</sup>                         | 78.8  |       |     |                  |

|                                         |                                | Differential input, 12-bit setting, –6 dBFS <sup>(1)</sup>                         | 88.9  |       |     |                  |

| CMRR                                    | Common-mode rejection ratio    | Differential input, 12-bit setting, 1-kHz sine (0 dBFS), limited by ADC resolution |       | >84   |     | dB               |

| Crosstalk                               |                                | Single ended input, 12-bit setting, 1-kHz sine (0 dBFS), limited by ADC resolution |       | >84   |     | dB               |

| Offset                                  |                                | Midscale                                                                           |       | –3    |     | $\text{mV}$      |

| Gain error                              |                                |                                                                                    |       | 0.68% |     |                  |

| DNL                                     | Differential nonlinearity      | 12-bit setting, mean <sup>(1)</sup>                                                | 0.05  |       |     | LSB              |

|                                         |                                | 12-bit setting, maximum <sup>(1)</sup>                                             | 0.9   |       |     |                  |

| INL                                     | Integral nonlinearity          | 12-bit setting, mean <sup>(1)</sup>                                                | 4.6   |       |     | LSB              |

|                                         |                                | 12-bit setting, maximum <sup>(1)</sup>                                             | 13.3  |       |     |                  |

|                                         |                                | 12-bit setting, mean, clocked by RCOSC                                             | 10    |       |     |                  |

|                                         |                                | 12-bit setting, max, clocked by RCOSC                                              | 29    |       |     |                  |

| SINAD<br>(-THD+N)                       | Signal-to-noise-and-distortion | Single ended input, 7-bit setting <sup>(1)</sup>                                   | 35.4  |       |     | dB               |

|                                         |                                | Single ended input, 9-bit setting <sup>(1)</sup>                                   | 46.8  |       |     |                  |

|                                         |                                | Single ended input, 10-bit setting <sup>(1)</sup>                                  | 57.5  |       |     |                  |

|                                         |                                | Single ended input, 12-bit setting <sup>(1)</sup>                                  | 66.6  |       |     |                  |

|                                         |                                | Differential input, 7-bit setting <sup>(1)</sup>                                   | 40.7  |       |     |                  |

|                                         |                                | Differential input, 9-bit setting <sup>(1)</sup>                                   | 51.6  |       |     |                  |

|                                         |                                | Differential input, 10-bit setting <sup>(1)</sup>                                  | 61.8  |       |     |                  |

|                                         |                                | Differential input, 12-bit setting <sup>(1)</sup>                                  | 70.8  |       |     |                  |

| Conversion time                         |                                | 7-bit setting                                                                      |       | 20    |     | $\mu\text{s}$    |

|                                         |                                | 9-bit setting                                                                      |       | 36    |     |                  |

|                                         |                                | 10-bit setting                                                                     |       | 68    |     |                  |

|                                         |                                | 12-bit setting                                                                     |       | 132   |     |                  |

(1) Measured with 300-Hz sine-wave input and VDD as reference.

## ADC CHARACTERISTICS (continued)

$T_A = 25^\circ\text{C}$  and  $VDD = 3\text{ V}$

| PARAMETER                                  | TEST CONDITIONS | MIN | TYP  | MAX | UNIT                         |

|--------------------------------------------|-----------------|-----|------|-----|------------------------------|

| Power consumption                          |                 |     | 1.2  |     | mA                           |

| Internal reference $VDD$ coefficient       |                 |     | 4    |     | $\text{mV/V}$                |

| Internal reference temperature coefficient |                 |     | 0.4  |     | $\text{mV}/10^\circ\text{C}$ |

| Internal reference voltage                 |                 |     | 1.24 |     | V                            |

## CONTROL INPUT AC CHARACTERISTICS

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $VDD = 2\text{ V}$  to  $3.6\text{ V}$

| PARAMETER                                                                      | TEST CONDITIONS                                                                                                                                                                                                                    | MIN | TYP | MAX | UNIT          |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| System clock, $f_{\text{SYSCLK}}$<br>$t_{\text{SYSCLK}} = 1/f_{\text{SYSCLK}}$ | The undivided system clock is 32 MHz when crystal oscillator is used. The undivided system clock is 16 MHz when calibrated 16-MHz RC oscillator is used.                                                                           | 16  | 32  |     | MHz           |

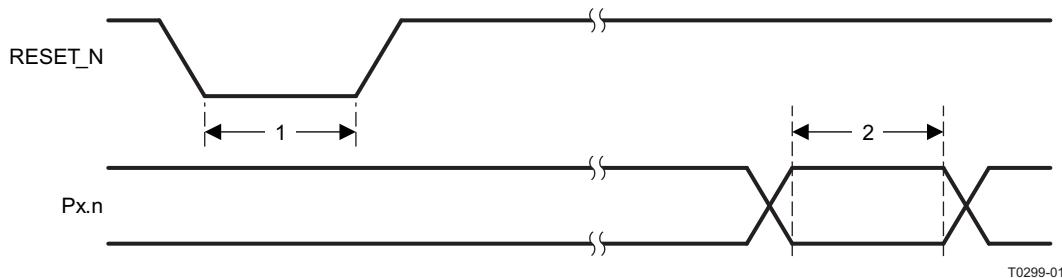

| RESET_N low duration                                                           | See item 1, <a href="#">Figure 2</a> . This is the shortest pulse that is recognized as a complete reset pin request. Note that shorter pulses may be recognized but do not lead to complete reset of all modules within the chip. | 1   |     |     | $\mu\text{s}$ |

| Interrupt pulse duration                                                       | See item 2, <a href="#">Figure 2</a> . This is the shortest pulse that is recognized as an interrupt request.                                                                                                                      | 20  |     |     | ns            |

**Figure 2. Control Input AC Characteristics**

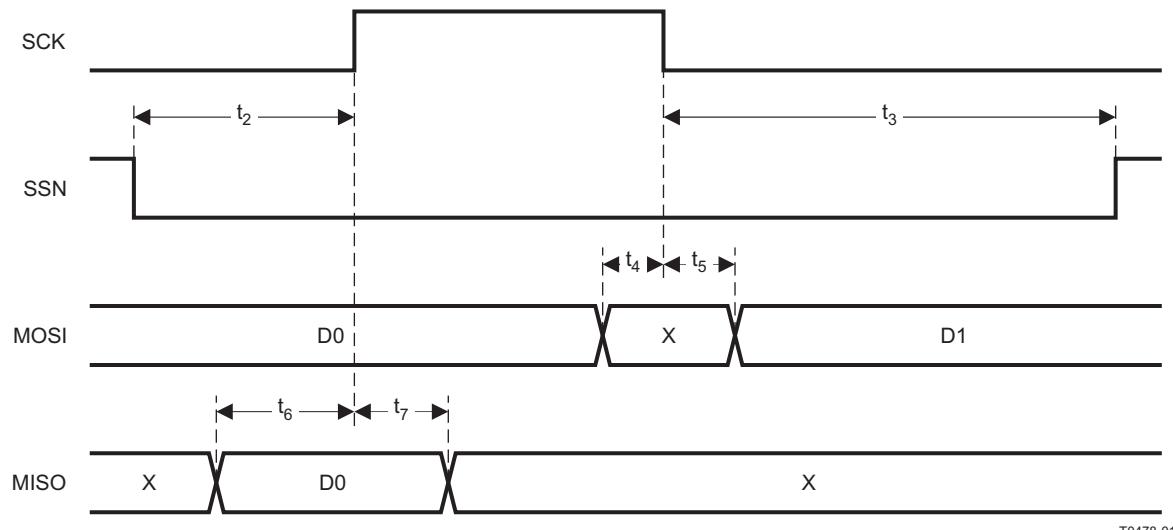

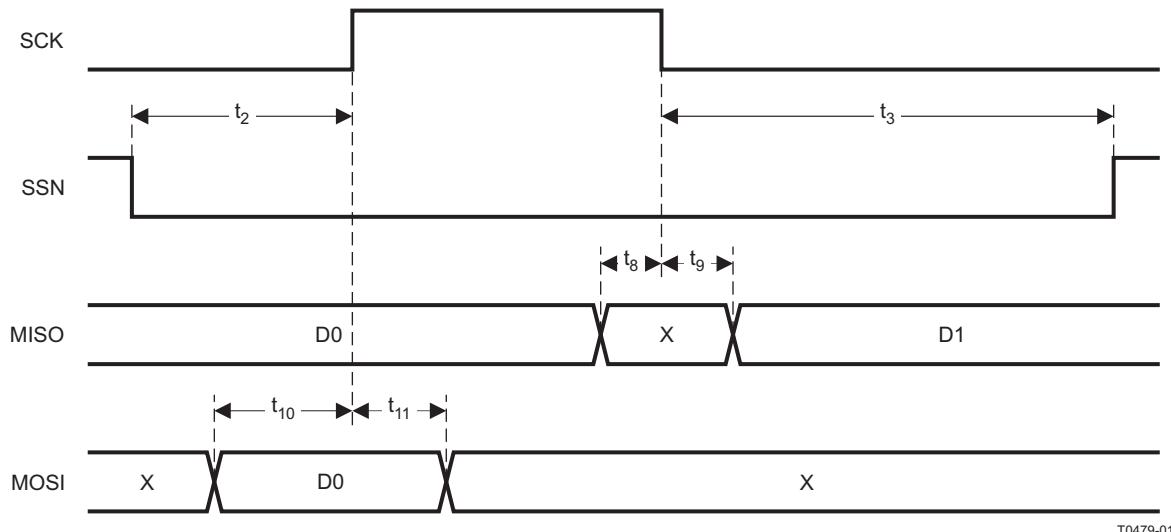

## SPI AC CHARACTERISTICS

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $VDD = 2\text{ V}$  to  $3.6\text{ V}$

| PARAMETER                | TEST CONDITIONS               | MIN | TYP | MAX | UNIT |

|--------------------------|-------------------------------|-----|-----|-----|------|

| $t_1$<br>SCK period      | Master, RX and TX             | 250 |     |     | ns   |

|                          | Slave, RX and TX              | 250 |     |     |      |

| SCK duty cycle           | Master                        |     | 50% |     |      |

| $t_2$<br>SSN low to SCK  | Master                        | 63  |     |     | ns   |

|                          | Slave                         | 63  |     |     |      |

| $t_3$<br>SCK to SSN high | Master                        | 63  |     |     | ns   |

|                          | Slave                         | 63  |     |     |      |

| $t_4$<br>MOSI early out  | Master, load = $10\text{ pF}$ |     | 7   |     | ns   |

| $t_5$<br>MOSI late out   | Master, load = $10\text{ pF}$ |     | 10  |     | ns   |

| $t_6$<br>MISO setup      | Master                        | 90  |     |     | ns   |

| $t_7$<br>MISO hold       | Master                        | 10  |     |     | ns   |

| SCK duty cycle           | Slave                         |     | 50% |     | ns   |

| $t_{10}$<br>MOSI setup   | Slave                         | 35  |     |     | ns   |

| $t_{11}$<br>MOSI hold    | Slave                         | 10  |     |     | ns   |

| $t_9$<br>MISO late out   | Slave, load = $10\text{ pF}$  |     | 95  |     | ns   |

| Operating frequency      | Master, TX only               |     | 8   |     | MHz  |

|                          | Master, RX and TX             |     | 4   |     |      |

|                          | Slave, RX only                |     | 8   |     |      |

|                          | Slave, RX and TX              |     | 4   |     |      |

**Figure 3. SPI Master AC Characteristics**

Figure 4. SPI Slave AC Characteristics

## DEBUG INTERFACE AC CHARACTERISTICS

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $VDD = 2\text{ V}$  to  $3.6\text{ V}$

| PARAMETER                                                                 | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

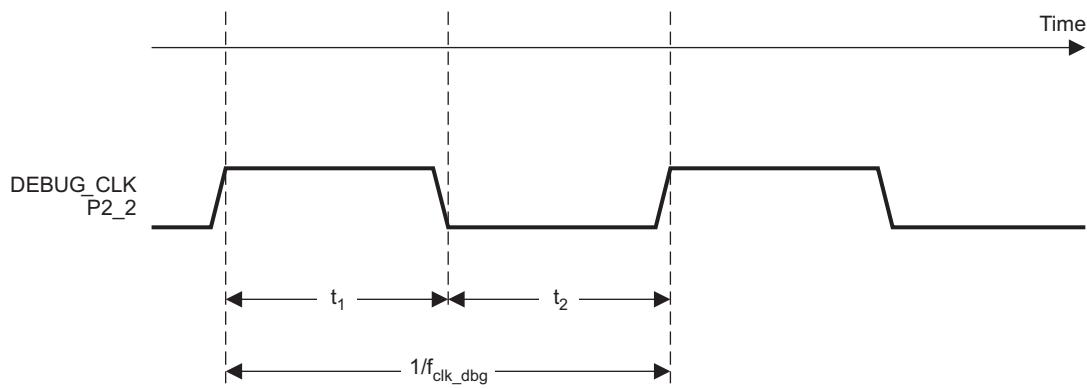

| $f_{\text{clk\_dbg}}$ Debug clock frequency (see Figure 5)                |                 |     |     | 12  | MHz  |

| $t_1$ Allowed high pulse on clock (see Figure 5)                          |                 | 35  |     |     | ns   |

| $t_2$ Allowed low pulse on clock (see Figure 5)                           |                 | 35  |     |     | ns   |

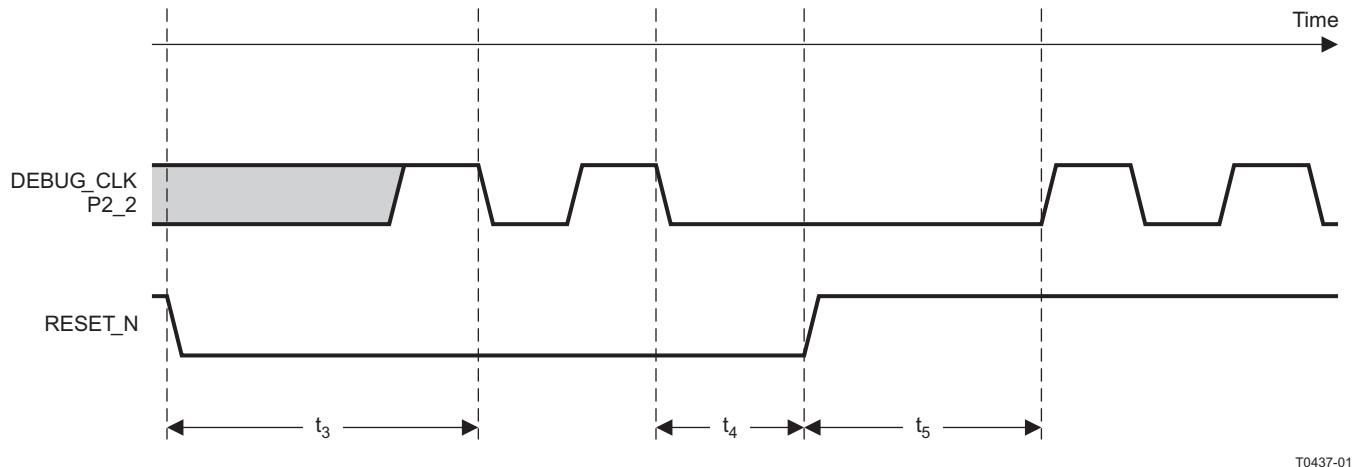

| $t_3$ EXT_RESET_N low to first falling edge on debug clock (see Figure 7) |                 | 167 |     |     | ns   |

| $t_4$ Falling edge on clock to EXT_RESET_N high (see Figure 7)            |                 | 83  |     |     | ns   |

| $t_5$ EXT_RESET_N high to first debug command (see Figure 7)              |                 | 83  |     |     | ns   |

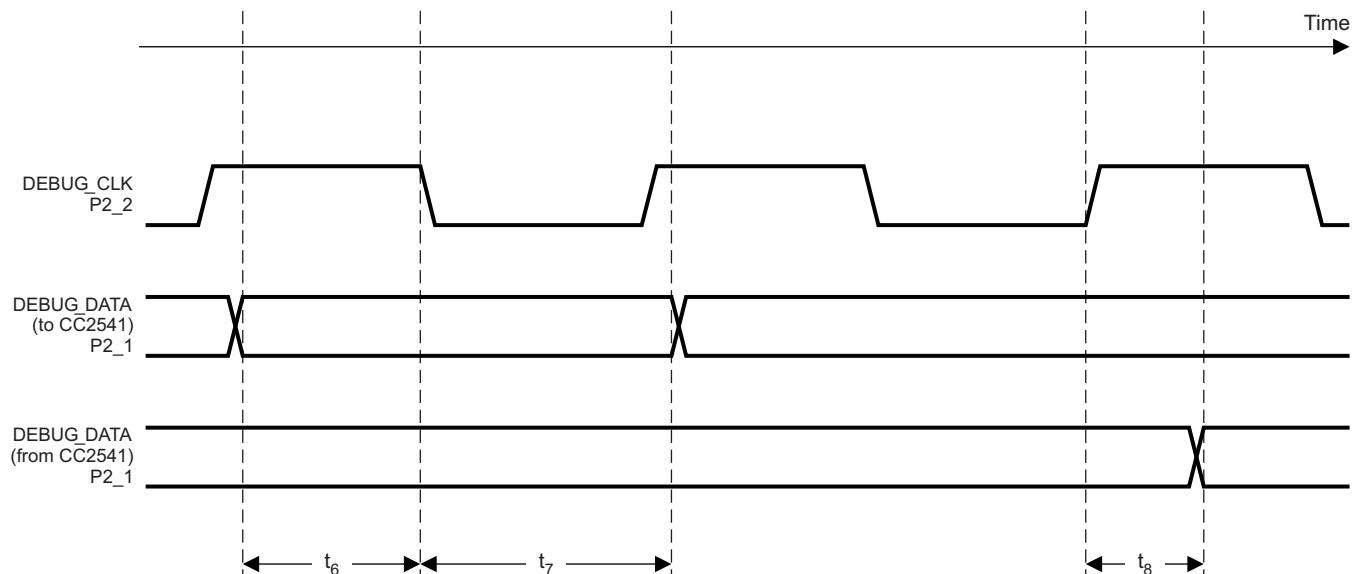

| $t_6$ Debug data setup (see Figure 6)                                     |                 | 2   |     |     | ns   |

| $t_7$ Debug data hold (see Figure 6)                                      |                 | 4   |     |     | ns   |

| $t_8$ Clock-to-data delay (see Figure 6)                                  | Load = 10 pF    |     | 30  |     | ns   |

Figure 5. Debug Clock – Basic Timing

**Figure 6. Debug Enable Timing**

**Figure 7. Data Setup and Hold Timing**

## TIMER INPUTS AC CHARACTERISTICS

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $VDD = 2\text{ V}$  to  $3.6\text{ V}$

| PARAMETER                    | TEST CONDITIONS                                                                                                                                         | MIN | TYP | MAX | UNIT                |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------------|

| Input capture pulse duration | Synchronizers determine the shortest input pulse that can be recognized. The synchronizers operate at the current system clock rate (16 MHz or 32 MHz). |     | 1.5 |     | $t_{\text{SYSCLK}}$ |

## DC CHARACTERISTICS

$T_A = 25^\circ\text{C}$ ,  $VDD = 3\text{ V}$

| PARAMETER                             | TEST CONDITIONS    | MIN | TYP | MAX | UNIT       |

|---------------------------------------|--------------------|-----|-----|-----|------------|

| Logic-0 input voltage                 |                    |     |     | 0.5 | V          |

| Logic-1 input voltage                 |                    |     |     | 2.4 | V          |

| Logic-0 input current                 | Input equals 0 V   |     |     | -50 | nA         |

| Logic-1 input current                 | Input equals $VDD$ |     |     | -50 | nA         |

| I/O-pin pullup and pulldown resistors |                    |     |     | 20  | k $\Omega$ |

| Logic-0 output voltage, 4- mA pins    | Output load 4 mA   |     |     | 0.5 | V          |

| Logic-1 output voltage, 4-mA pins     | Output load 4 mA   |     |     | 2.5 | V          |

| Logic-0 output voltage, 20- mA pins   | Output load 20 mA  |     |     | 0.5 | V          |

| Logic-1 output voltage, 20-mA pins    | Output load 20 mA  |     |     | 2.5 | V          |

## DEVICE INFORMATION

### PIN DESCRIPTIONS

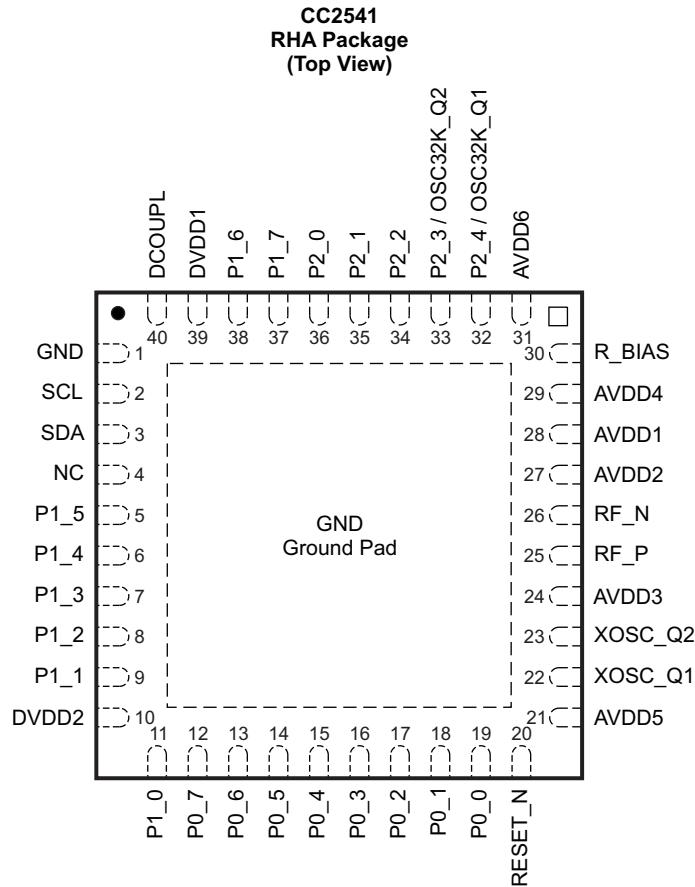

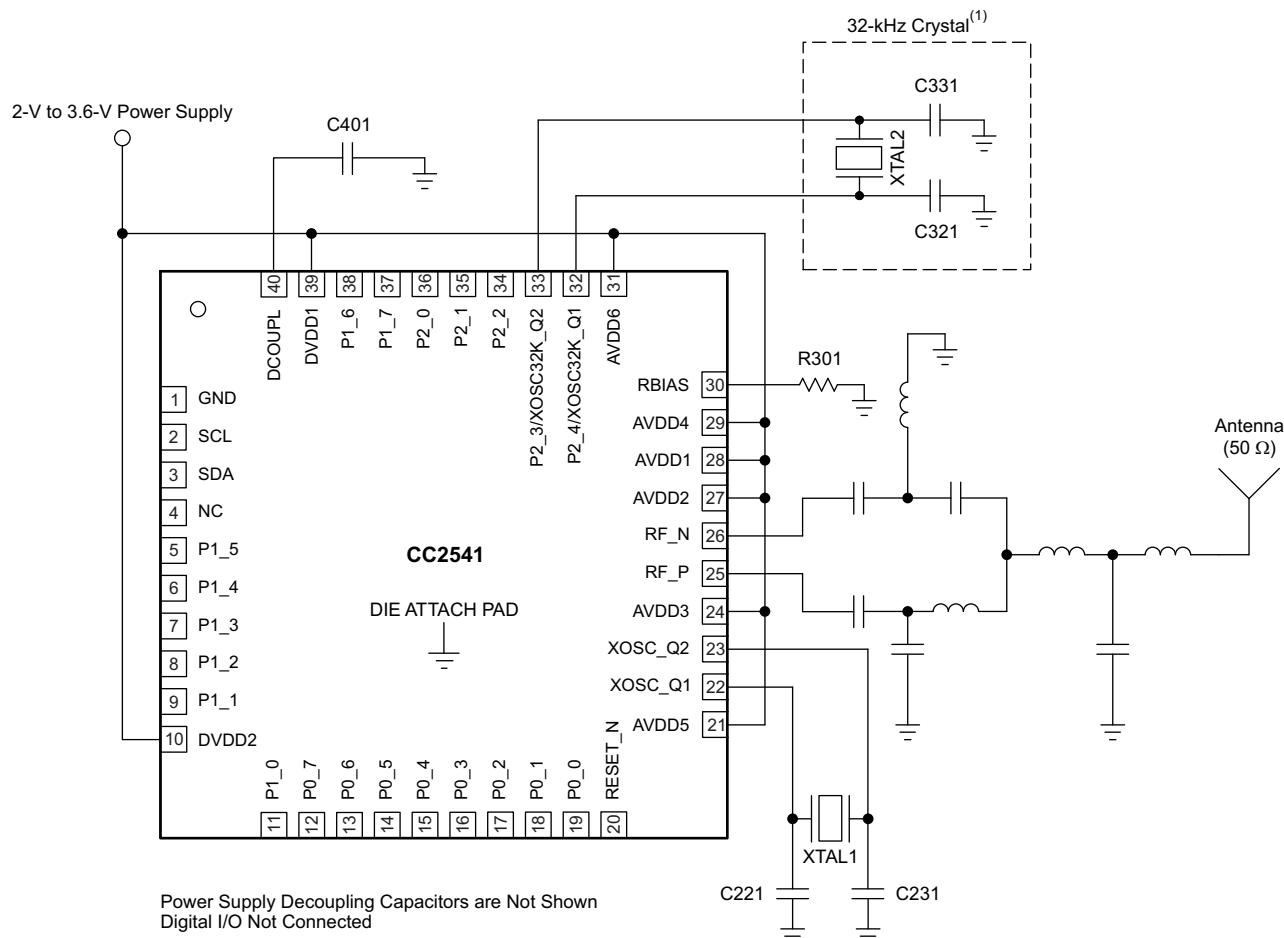

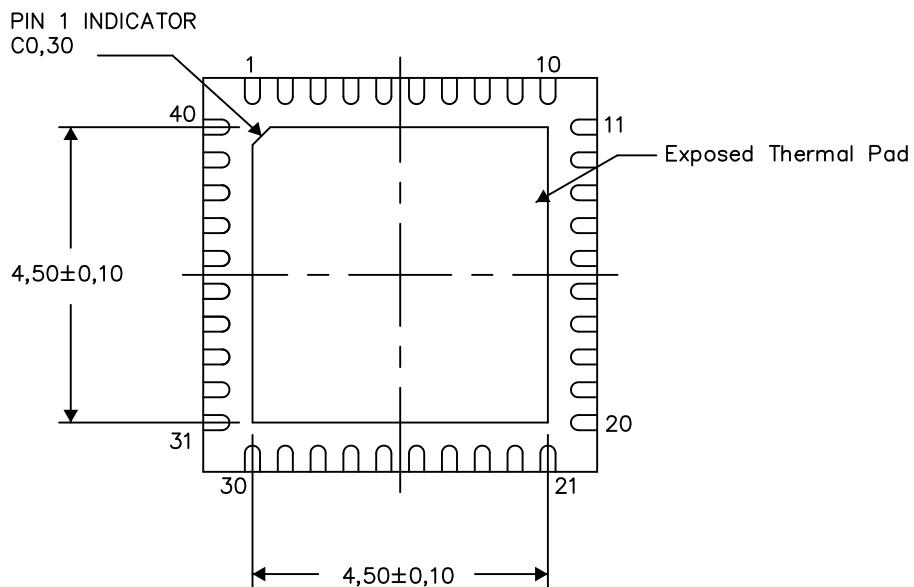

The CC2541 pinout is shown in [Figure 8](#) and a short description of the pins follows.

NOTE: The exposed ground pad must be connected to a solid ground plane, as this is the ground connection for the chip.

**Figure 8. Pinout Top View**

**PIN DESCRIPTIONS**

| PIN NAME           | PIN | PIN TYPE                              | DESCRIPTION                                                                                                       |

|--------------------|-----|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| AVDD1              | 28  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| AVDD2              | 27  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| AVDD3              | 24  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| AVDD4              | 29  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| AVDD5              | 21  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| AVDD6              | 31  | Power (analog)                        | 2-V–3.6-V analog power-supply connection                                                                          |

| DCOUP1             | 40  | Power (digital)                       | 1.8-V digital power-supply decoupling. Do not use for supplying external circuits.                                |

| DVDD1              | 39  | Power (digital)                       | 2-V–3.6-V digital power-supply connection                                                                         |

| DVDD2              | 10  | Power (digital)                       | 2-V–3.6-V digital power-supply connection                                                                         |

| GND                | 1   | Ground pin                            | Connect to GND                                                                                                    |

| GND                | —   | Ground                                | The ground pad must be connected to a solid ground plane.                                                         |

| NC                 | 4   | Unused pins                           | Not connected                                                                                                     |

| P0_0               | 19  | Digital I/O                           | Port 0.0                                                                                                          |

| P0_1               | 18  | Digital I/O                           | Port 0.1                                                                                                          |

| P0_2               | 17  | Digital I/O                           | Port 0.2                                                                                                          |

| P0_3               | 16  | Digital I/O                           | Port 0.3                                                                                                          |

| P0_4               | 15  | Digital I/O                           | Port 0.4                                                                                                          |

| P0_5               | 14  | Digital I/O                           | Port 0.5                                                                                                          |

| P0_6               | 13  | Digital I/O                           | Port 0.6                                                                                                          |

| P0_7               | 12  | Digital I/O                           | Port 0.7                                                                                                          |

| P1_0               | 11  | Digital I/O                           | Port 1.0 – 20-mA drive capability                                                                                 |

| P1_1               | 9   | Digital I/O                           | Port 1.1 – 20-mA drive capability                                                                                 |

| P1_2               | 8   | Digital I/O                           | Port 1.2                                                                                                          |

| P1_3               | 7   | Digital I/O                           | Port 1.3                                                                                                          |

| P1_4               | 6   | Digital I/O                           | Port 1.4                                                                                                          |

| P1_5               | 5   | Digital I/O                           | Port 1.5                                                                                                          |

| P1_6               | 38  | Digital I/O                           | Port 1.6                                                                                                          |

| P1_7               | 37  | Digital I/O                           | Port 1.7                                                                                                          |

| P2_0               | 36  | Digital I/O                           | Port 2.0                                                                                                          |

| P2_1/DD            | 35  | Digital I/O                           | Port 2.1 / debug data                                                                                             |

| P2_2/DC            | 34  | Digital I/O                           | Port 2.2 / debug clock                                                                                            |

| P2_3/<br>OSC32K_Q2 | 33  | Digital I/O, Analog I/O               | Port 2.3/32.768 kHz XOSC                                                                                          |

| P2_4/<br>OSC32K_Q1 | 32  | Digital I/O, Analog I/O               | Port 2.4/32.768 kHz XOSC                                                                                          |

| RBIAS              | 30  | Analog I/O                            | External precision bias resistor for reference current                                                            |

| RESET_N            | 20  | Digital input                         | Reset, active-low                                                                                                 |

| RF_N               | 26  | RF I/O                                | Negative RF input signal to LNA during RX<br>Negative RF output signal from PA during TX                          |

| RF_P               | 25  | RF I/O                                | Positive RF input signal to LNA during RX<br>Positive RF output signal from PA during TX                          |

| SCL                | 2   | I <sup>2</sup> C clock or digital I/O | Can be used as I <sup>2</sup> C clock pin or digital I/O. Leave floating if not used. If grounded disable pull up |

| SDA                | 3   | I <sup>2</sup> C clock or digital I/O | Can be used as I <sup>2</sup> C data pin or digital I/O. Leave floating if not used. If grounded disable pull up  |

| XOSC_Q1            | 22  | Analog I/O                            | 32-MHz crystal oscillator pin 1 or external clock input                                                           |